(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2015/171699 A1

(43) International Publication Date 12 November 2015 (12.11.2015)

(51) International Patent Classification: *G02B 6/26* (2006.01) *B05D 5/06* (2006.01)

(21) International Application Number:

PCT/US2015/029373

(22) International Filing Date:

6 May 2015 (06.05.2015)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/989,904

7 May 2014 (07.05.2014)

US

- (71) Applicant: PRESIDENT AND FELLOWS OF HAR-VARD COLLEGE [US/US]; 17 Quincy Street, Cambridge, MA 02138 (US).

- (72) Inventors: LIEBER, Charles, M.; 27 Hayes Avenue, Lexington, MA 02420 (US). DAY, Robert; 36 Lincoln Parkway, Apt.#2, Somerville, MA 02143 (US). MANKIN, Max, Nathan; 11 Everett Street, Cambridge, MA 02138 (US). GAO, Ruixuan; 36 Lincoln Parkway, Somerville, MA 02143 (US). KEMPA, Thomas, J.; 40 Howard Street, Unit 6, Somerville, MA 02144 (US).

- (74) Agent: CHEN, Tani; Wolf, Greenfield & Sacks, P.C., 600 Atlantic Avenue, Boston, MA 02210-2206 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

### (54) Title: CONTROLLED GROWTH OF NANOSCALE WIRES

Fig. 1A

(57) Abstract: The present invention generally relates to nanoscale wires, and to methods of producing nanoscale wires. In some aspects, the nanoscale wires are nanowires comprising a core which is continuous and a shell which may be continuous or discontinuous, and/or may have regions having different cross-sectional areas. In some embodiments, the shell regions are produced by passing the shell material (or a precursor thereof) over a core nanoscale wire under conditions in which Plateau-Raleigh crystal growth occurs, which can lead to non-homogenous deposition of the shell material on different regions of the core. The core and the shell each independently may comprise semiconductors, and/or non-semiconductor materials such as semiconductor oxides, metals, polymers, or the like. Other embodiments are generally directed to systems and methods of making or using such nanoscale wires, devices containing such nanoscale wires, or the like.

- 1 -

# **CONTROLLED GROWTH OF NANOSCALE WIRES**

### RELATED APPLICATIONS

This application claims the benefit of U.S. Provisional Patent Application Serial No. 61/989,904, filed May 7, 2014, entitled "Controlled Growth of Nanoscale Wires," by Lieber, *et al.*, incorporated herein by reference in its entirety.

#### **GOVERNMENT FUNDING**

This invention was made with government support under Grant No. N00244-09-1-0078 awarded by Department of Defense, Office of Naval Research. The government has certain rights in the invention.

#### FIELD

The present invention generally relates to nanoscale wires, and to methods of producing nanoscale wires.

10

25

30

#### **BACKGROUND**

Interest in nanotechnology, in particular sub-microelectronic technologies such as semiconductor quantum dots and nanowires, has been motivated by the challenges of chemistry and physics at the nanoscale, and by the prospect of utilizing these structures in electronic and related devices. Nanoscopic articles might be well-suited for transport of charge carriers and excitons (e.g. electrons, electron pairs, etc.) and thus may be useful as building blocks in nanoscale applications.

#### **SUMMARY**

The present invention generally relates to nanoscale wires, and to methods of producing nanoscale wires. The subject matter of the present invention involves, in some cases, interrelated products, alternative solutions to a particular problem, and/or a plurality of different uses of one or more systems and/or articles.

In one aspect, the present invention is generally directed to an article, such as a nanoscale wire. In some cases, the nanoscale wire is a nanowire. For example, in one set of embodiments, the article comprises a nanowire comprising a continuous core comprising a first longitudinal portion comprising a shell at least partially surrounding the core and having a substantially constant cross-sectional area, and a second longitudinal portion having a substantially constant cross-section area smaller than the first longitudinal portion. In some embodiments, the first longitudinal portion has a first

- 2 -

dimension orthogonal to the core and a second dimension orthogonal to the first dimension and to the core, where an aspect ratio of the first dimension to the second dimension is at least about 1.5:1. In certain cases, the core and the shell material have different compositions.

In another set of embodiments, the article comprises a nanowire comprising a continuous semiconductor oxide core and a plurality of discontinuous semiconductor shell regions.

5

10

15

20

25

30

The article, in yet another set of embodiments, comprises a nanowire comprising a continuous semiconductor oxide core comprising a first longitudinal portion having a length of at least 5 nm and a first substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm a second substantially constant cross-section area smaller than the first longitudinal portion, and a transitional portion between the first longitudinal portion and the second longitudinal portion, the transitional portion having a length of at least about 10 nm.

According to still another set of embodiments, the article comprises a nanowire comprising a continuous core and a plurality of discontinuous shell regions. In some cases, some or all of the discontinuous shell regions each consist of a single crystal.

In one set of embodiments, the article comprises a nanowire comprising a continuous core and a plurality of discontinuous shell regions. In some cases, the discontinuous shell regions each consist of a single crystal.

The article, in another set of embodiments, includes a nanowire comprising a continuous metallic core and a plurality of discontinuous semiconductor shell regions.

In yet another set of embodiments, the article comprises a nanowire comprising a continuous polymeric core and a plurality of discontinuous semiconductor shell regions.

According to still another set of embodiments, the article comprises a nanowire comprising a continuous core and a plurality of discontinuous shell regions. In some embodiments, the discontinuous shell regions each comprise a plurality of nanoparticles.

The article, in another set of embodiments, includes a nanowire comprising a continuous semiconductor oxide core comprising a first longitudinal portion having a length of at least 5 nm and a substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm and a substantially constant cross-section area smaller than the first longitudinal portion. In some embodiments, the first

- 3 -

longitudinal portion has a first dimension orthogonal to the core and a second dimension orthogonal to the first dimension and to the core. In certain cases, an aspect ratio of the first dimension to the second dimension is at least about 1.5:1.

The article, in yet another set of embodiments, comprises a nanowire comprising a continuous metallic core comprising a first longitudinal portion having a length of at least 5 nm and a first substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm a second substantially constant cross-section area smaller than the first longitudinal portion, and a transitional portion between the first longitudinal portion and the second longitudinal portion, the transitional portion having a length of at least about 10 nm.

5

10

15

20

25

30

In still another set of embodiments, the article includes a nanowire comprising a continuous metallic core comprising a first longitudinal portion having a length of at least 5 nm and a substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm and a substantially constant cross-section area smaller than the first longitudinal portion. In some cases, the first longitudinal portion has a first dimension orthogonal to the core and a second dimension orthogonal to the first dimension to the second dimension is at least about 1.5:1.

According to yet another set of embodiments, the article comprises a nanowire comprising a continuous polymeric core comprising a first longitudinal portion having a length of at least 5 nm and a first substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm a second substantially constant cross-section area smaller than the first longitudinal portion, and a transitional longitudinal portion between the first longitudinal portion and the second longitudinal portion, the transitional portion having a length of at least about 10 nm.

In another set of embodiments, the article comprises a nanowire comprising a continuous polymeric core comprising a first longitudinal portion having a length of at least 5 nm and a substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm and a substantially constant cross-section area smaller than the first longitudinal portion. In some cases, the first longitudinal portion has a first dimension orthogonal to the core and a second dimension orthogonal to the first

- 4 -

dimension and to the core. In some embodiments, an aspect ratio of the first dimension to the second dimension is at least about 1.5:1.

In accordance with another set of embodiments, the article includes a nanowire comprising a continuous core comprising a first longitudinal portion comprising a shell at least partially surrounding the core having a length of at least 5 nm and a substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm and a substantially constant cross-section area smaller than the first longitudinal portion, and a transitional longitudinal portion between the first longitudinal portion and the second longitudinal portion, where the transitional portion has a length of at least about 10 nm. In some embodiments, the core and the shell material comprise different materials.

5

10

15

20

25

30

The article, in yet another set of embodiments, comprises a nanowire comprising a continuous core comprising a first longitudinal portion having a length of at least 5 nm and a first substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm a second substantially constant cross-section area smaller than the first longitudinal portion, and a transitional longitudinal portion between the first longitudinal portion and the second longitudinal portion, the transitional longitudinal having a length of at least about 10 nm.

According to still another set of embodiments, the article comprises a nanowire comprising a continuous core comprising a first longitudinal portion having a length of at least 5 nm and a substantially constant cross-sectional area, a second longitudinal portion having a length of at least 5 nm and a substantially constant cross-section area smaller than the first longitudinal portion. In some embodiments, the first longitudinal portion has a first dimension orthogonal to the core and a second dimension orthogonal to the first dimension and to the core. In certain cases, an aspect ratio of the first dimension to the second dimension is at least about 1.5:1.

In another set of embodiments, the present invention is generally directed to a nanowire comprising a core and at least one shell, e.g., as discussed herein. The core may comprise a metal, a semiconductor, a semiconductor oxide, a polymer, particles, or the like. The shell may independently be a semiconductor, a metal, a polymer, an oxide, an insulator, a dielectric, and/or the shell may comprise particles. Thus, for example, the core may comprise a metal and the shell may comprise a semiconductor, or the core may

5

10

15

20

25

30

- 5 -

comprise a metal and the shell may comprise a metal, or the core may comprise a metal and the shell may comprise a polymer, or the core may comprise a metal and the shell may comprise a semiconductor oxide, or the core may comprise a metal and the shell may comprise a semiconductor, or the core may comprise a metal and the shell may comprise an insulator, or the core may comprise a metal and the shell may comprise a dielectric, or the core may comprise a metal and the shell may comprise particles, or the core may comprise a semiconductor and the shell may comprise a semiconductor, or the core may comprise a semiconductor and the shell may comprise a metal, or the core may comprise a semiconductor and the shell may comprise a polymer, or the core may comprise a semiconductor and the shell may comprise a semiconductor oxide, or the core may comprise a semiconductor and the shell may comprise a semiconductor, or the core may comprise a semiconductor and the shell may comprise an insulator, or the core may comprise a semiconductor and the shell may comprise a dielectric, or the core may comprise a semiconductor and the shell may comprise particles, or the core may comprise a semiconductor oxide and the shell may comprise a semiconductor, or the core may comprise a semiconductor oxide and the shell may comprise a metal, or the core may comprise a semiconductor oxide and the shell may comprise a polymer, or the core may comprise a semiconductor oxide and the shell may comprise a semiconductor oxide, or the core may comprise a semiconductor oxide and the shell may comprise a semiconductor, or the core may comprise a semiconductor oxide and the shell may comprise an insulator, or the core may comprise a semiconductor oxide and the shell may comprise a dielectric, or the core may comprise a semiconductor oxide and the shell may comprise particles, or the core may comprise a polymer and the shell may comprise a semiconductor, or the core may comprise a polymer and the shell may comprise a metal, or the core may comprise a polymer and the shell may comprise a polymer, or the core may comprise a polymer and the shell may comprise a semiconductor oxide, or the core may comprise a polymer and the shell may comprise a semiconductor, or the core may comprise a polymer and the shell may comprise an insulator, or the core may comprise a polymer and the shell may comprise a dielectric, or the core may comprise a polymer and the shell may comprise particles, etc.

In addition, the present invention, in some aspects, is generally directed to systems and methods for making a nanoscale wire. In some cases, the nanoscale wire is

a nanowire. In one set of embodiments, for example, the method includes acts of depositing a shell material on a nanowire by flowing a fluid comprising the shell material or a precursor thereof over the nanowire at a flowrate of less than about 10 sccm at a temperature of between about 700 °C and about 900 °C and under a pressure of less than about 1 torr. The fluid may be a liquid or a gas (or the fluid may comprise both a liquid and a gas, in some cases).

5

10

15

20

25

30

According to another set of embodiments, the method includes an act of depositing a shell material on a nanowire by flowing a fluid comprising the shell material or a precursor thereof over the nanowire such that the surface diffusion length of the shell material on the surface of the nanowire is at least about 100 nm.

In still another set of embodiments, the method includes an act of depositing a shell material on a nanowire by flowing a fluid comprising the shell material (or a precursor thereof) over the nanowire at a flowrate of less than about 10 sccm at a temperature of between about 700 °C and about 900 °C and under a pressure of less than about 1 torr. In some cases, the flowrate may be less than about 20 sccm. In some cases, the fluid flows longitudinally over the nanowire.

The method, in yet another set of embodiments, includes an act of depositing a shell material (or a precursor thereof) on a nanowire by flowing a fluid comprising the shell material over the nanowire such that the surface diffusion length of the shell material on the surface of the nanowire is at least about 100 nm. In some cases, the fluid flows longitudinally over the nanowire.

In one set of embodiments, the method includes an act of flowing a fluid, such as a liquid and/or a gas, comprising a shell material (or a precursor thereof) over a nanowire such that the shell material deposits on the nanowire in a plurality of discontinuous shell regions. In some cases, the fluid flows longitudinally over the nanowire.

The method, in accordance with another set of embodiments, includes an act of depositing a shell material (or a precursor thereof) on a nanowire by flowing a fluid, such as a liquid and/or a gas, comprising the shell material over the nanowire under Plateau-Raleigh crystal growth conditions. In some cases, the fluid flows longitudinally over the nanowire.

The method, in still another set of embodiments, includes an act of depositing a shell material (or a precursor thereof) on a nanowire by flowing a fluid, such as a liquid

- 7 -

and/or a gas, comprising the shell material over the nanowire such that the shell material is able to minimize its surface area. In some cases, the fluid flows longitudinally over the nanowire.

In yet another set of embodiments, the method includes an act of thermally evaporating a shell material (or a precursor thereof) onto a nanowire such that the shell material deposits on the nanowire in a plurality of discontinuous shell regions. In yet another set of embodiments, the method includes an act of depositing a shell material (or a precursor thereof) onto a nanowire via physical vapor deposition such that the shell material deposits on the nanowire in a plurality of discontinuous shell regions.

5

10

15

20

25

30

According to still another set of embodiments, the method includes an act of depositing a shell material (or a precursor thereof) on a nanowire by flowing a fluid comprising the shell material over the nanowire such that the shell material is able to minimize its surface area. In some cases, the fluid flows longitudinally over the nanowire.

The method, in yet another set of embodiments, comprises an act of depositing a shell material (or a precursor thereof) on a nanowire by flowing a fluid comprising the shell material over the nanowire under Plateau-Raleigh crystal growth conditions. In some cases, the fluid flows longitudinally over the nanowire.

In one set of embodiments, the method includes an act of flowing a fluid comprising a shell material (or a precursor thereof) over a nanowire such that the shell material deposits on the nanowire in a plurality of discontinuous shell regions. In some cases, the fluid flows longitudinally over the nanowire.

In another aspect, the present invention encompasses methods of making one or more of the embodiments described herein, for example, nanoscale wires. In still another aspect, the present invention encompasses methods of using one or more of the embodiments described herein, for example, nanoscale wires.

Other advantages and novel features of the present invention will become apparent from the following detailed description of various non-limiting embodiments of the invention when considered in conjunction with the accompanying figures. In cases where the present specification and a document incorporated by reference include conflicting and/or inconsistent disclosure, the present specification shall control. If two or more documents incorporated by reference include conflicting and/or inconsistent

5

10

disclosure with respect to each other, then the document having the later effective date shall control.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

- Non-limiting embodiments of the present invention will be described by way of example with reference to the accompanying figures, which are schematic and are not intended to be drawn to scale. In the figures, each identical or nearly identical component illustrated is typically represented by a single numeral. For purposes of clarity, not every component is labeled in every figure, nor is every component of each embodiment of the invention shown where illustration is not necessary to allow those of ordinary skill in the art to understand the invention. In the figures:

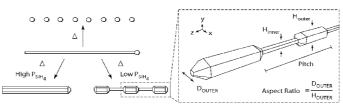

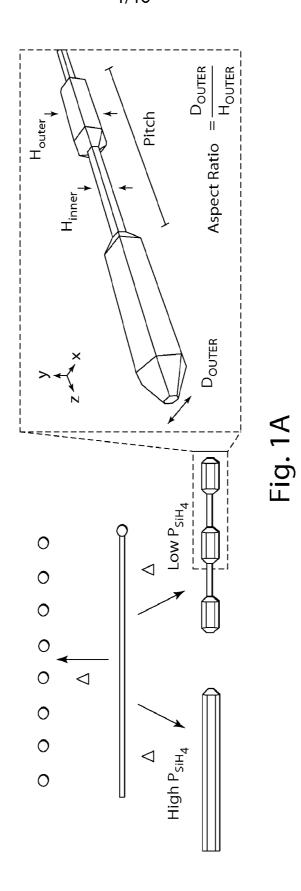

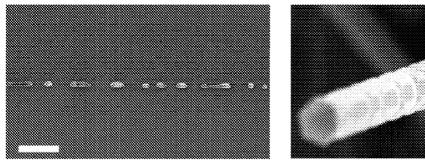

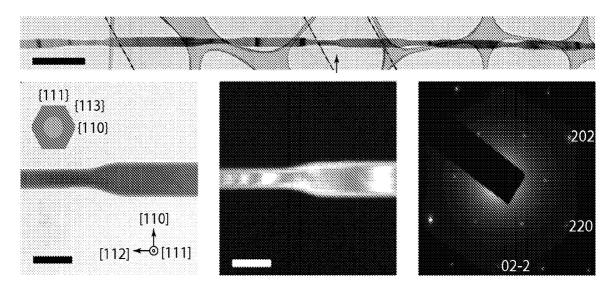

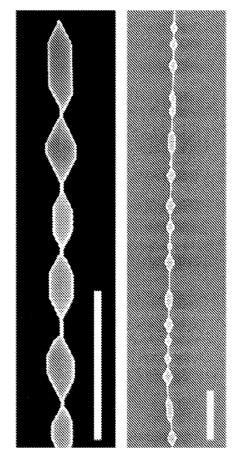

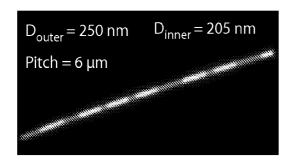

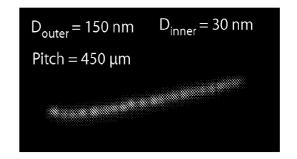

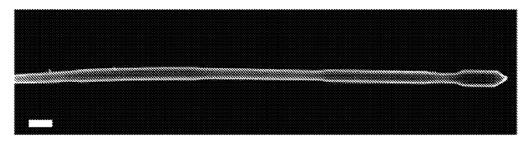

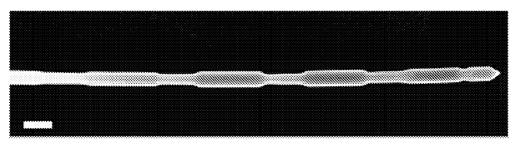

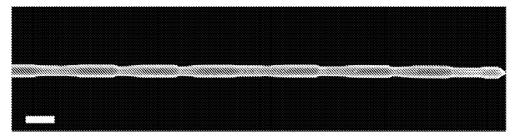

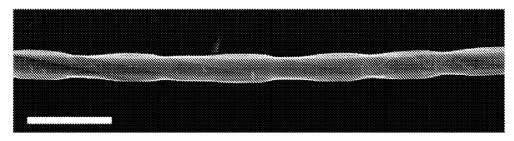

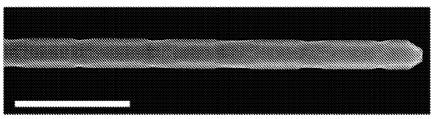

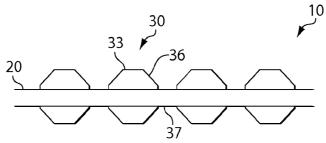

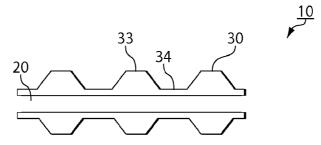

- Figs. 1A-1D illustrate Plateau-Raleigh crystal growth, in certain embodiments of the invention;

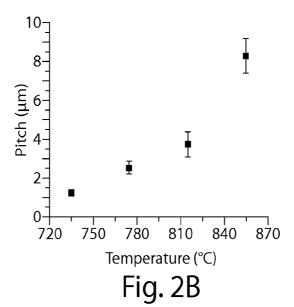

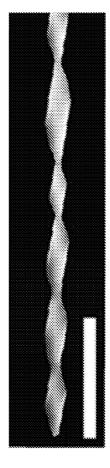

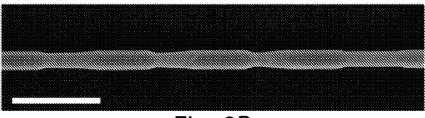

- Figs. 2A-2D illustrate control of Plateau-Raleigh crystal growth, according to some embodiments of the invention;

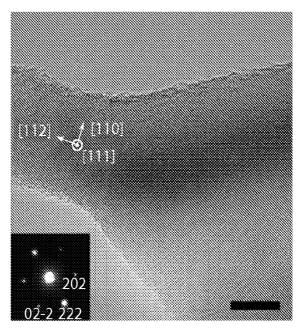

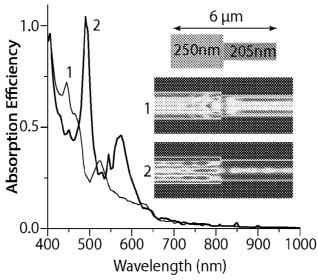

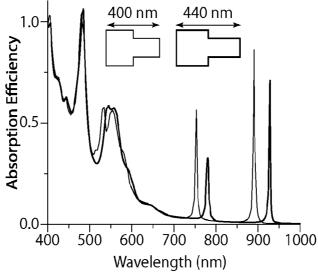

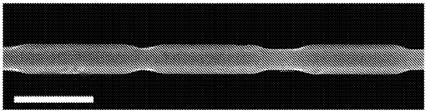

- Figs. 3A-3D illustrate various nanoscale wires, in some embodiments of the invention;

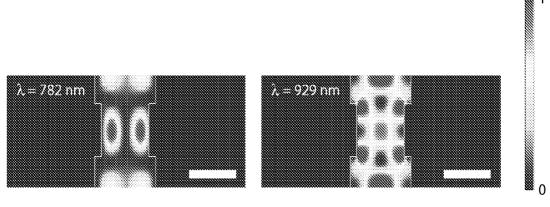

- Figs. 4A-4C illustrate optical properties of certain nanoscale wires, in certain embodiments of the invention;

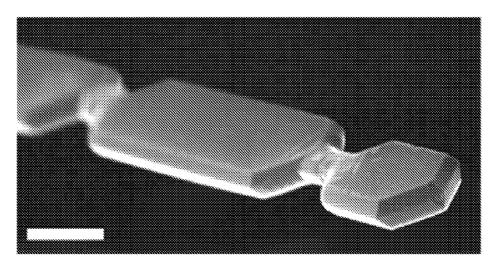

- Fig. 5 illustrates a silicon nanoscale wire;

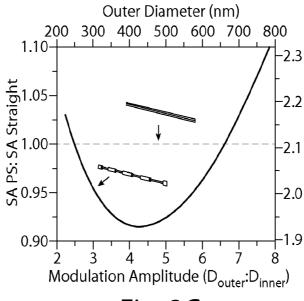

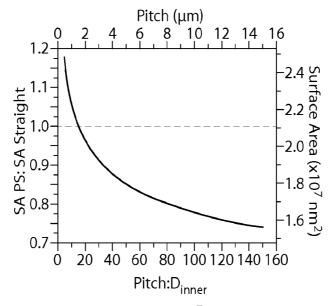

- Figs. 6A-6B illustrate various diameter-modulated nanoscale wires, in some embodiments of the invention;

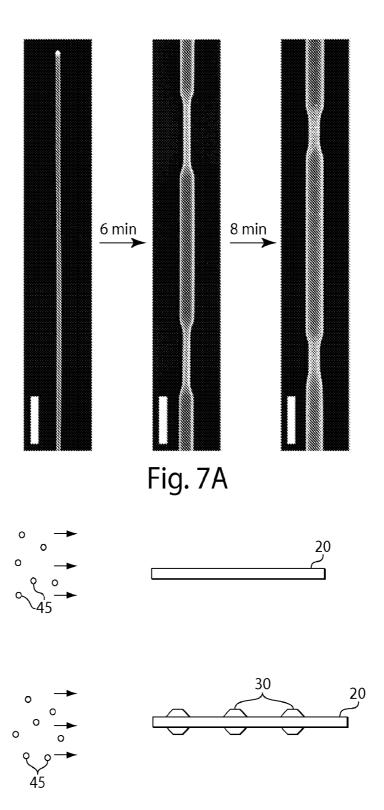

- Figs. 7A-7B illustrates a time sequence of Plateau-Raleigh crystal growth, in some embodiments of the invention:

- Figs. 8A-8D illustrate pitch as a function of flow rate, in some embodiments of the invention;

- Figs. 9A-9D illustrate pitch as a function of temperature, in certain embodiments of the invention;

- Fig. 10 is an SEM of a typical nanoscale wire in accordance with one embodiment of the invention;

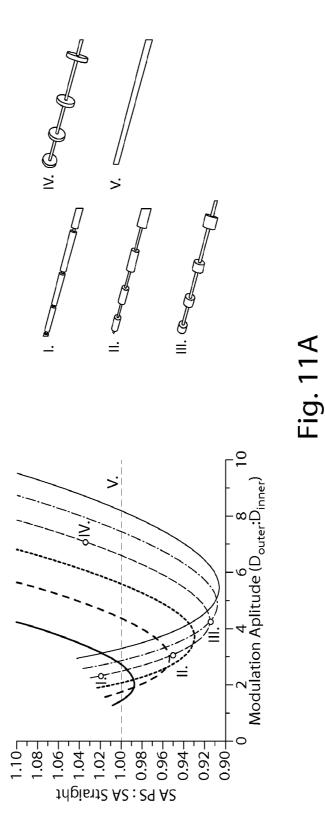

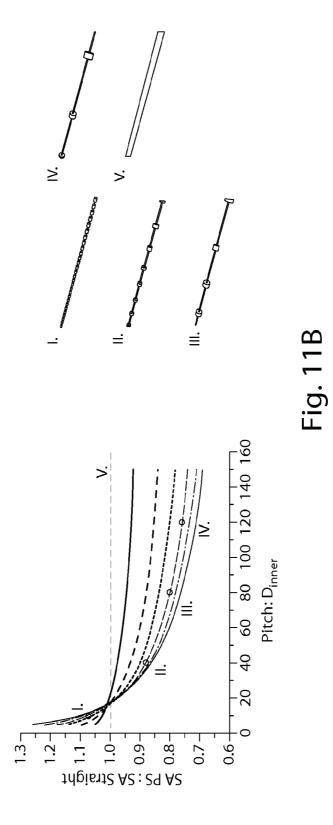

- Figs. 11A-11B illustrate surface area ratios in accordance with some embodiments of the invention:

- 9 -

Figs. 12A-12B illustrate absorption on certain nanoscale wires, in some embodiments of the invention;

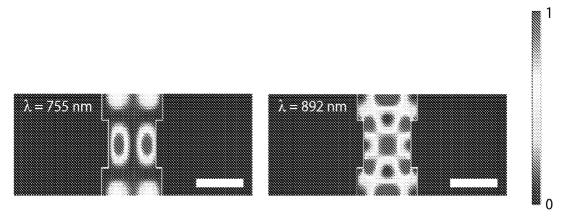

Figs. 13A-13C are schematic diagrams used for modeling, in certain embodiments of the invention; and

5

10

15

20

25

30

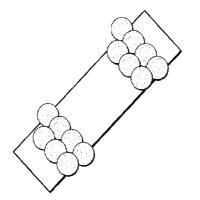

Fig. 14 is a schematic diagram of a nanoscale wire comprising nanoparticles.

### **DETAILED DESCRIPTION**

The present invention generally relates to nanoscale wires, and to methods of producing nanoscale wires. In some aspects, the nanoscale wires are nanowires comprising a core which is continuous and a shell which may be continuous or discontinuous, and/or may have regions having different cross-sectional areas. In some embodiments, the shell regions are produced by passing the shell material (or a precursor thereof) over a core nanoscale wire under conditions in which Plateau-Raleigh crystal growth occurs, which can lead to non-homogenous deposition of the shell material on different regions of the core. The core and the shell each independently may comprise semiconductors, and/or non-semiconductor materials such as semiconductor oxides, metals, polymers, or the like. Other embodiments are generally directed to systems and methods of making or using such nanoscale wires, devices containing such nanoscale wires, or the like.

Referring now to Fig. 13A, in one aspect, the present invention is generally directed to a nanoscale wire 10 having a core 20 and one or more shell regions 30. The core 20 may be a nanowire, and may comprise a semiconductor material (e.g., germanium, silicon, indium phosphide, etc.), a dielectric material such as a semiconductor oxide (e.g., silicon dioxide), a metal (e.g., Ni, Pt, Au, etc.), a polymer (e.g., polyaniline, polypyrrole, etc.), or the like. Other materials are discussed below. In some embodiments, the core has a substantially uniform cross-sectional area along the length of the core. The core can be prepared using techniques known to those of ordinary skill in the art, such as those discussed below.

There may also be a shell 30 surrounding at least part of the core 20. The shell may be formed from a semiconductor material, or other materials such as dielectric materials, semiconductor oxides, metals, polymers, nanoparticles, or the like. In some cases, the shell material is substantially crystalline, and in some cases, the shell material is substantially monocrystalline. The core may also be composed of crystallites in

- 10 -

certain cases. The shell may have the same or a different composition from than the core.

5

10

15

20

25

30

The shell may be present as discontinuous regions along core 20, as shown in Fig. 13A, or as a continuous region, but with portions having different cross-sectional areas. The shell may be cylindrically symmetrical around the core, as is shown in Fig. 13A, although in some cases, the shell may be non-cylindrically symmetrically distributed around the core, for example, as shown in Fig. 3D with the shell having a substantially rectangular cross-sectional area. In certain embodiments, the shell regions may be substantially regularly spaced along the core 20, and the average spacing or periodicity may be referred to as the "pitch" of the shells along the core. Thus, as a non-limiting example, the pitch of the shells along the core may be between about 5 nm and about 100 micrometers. In addition, it should also be understood that in reality, there may also be some deviations from perfect periodicity or perfect pitch.

In one set of embodiments, the shell may be grown around the core by flowing or passing the shell material 45, or a precursor thereof, along the core, as is shown in Fig. 7B. In some cases, shell material (or precursor) may be present within a fluid (e.g., a liquid, a gas, plasma, etc.), and in some cases, the fluid may be under relatively low pressures, as discussed below. As the fluid passes past core 20, some of the shell material 45 can deposit or form onto the core. Under certain conditions as discussed herein, instabilities may be created, such as in Plateau-Raleigh crystal growth. Without wishing to be bound by any theory, it is believed that under certain conditions, certain materials have a tendency to minimize surface area as they deposit onto a substrate. For example, under some flow conditions as discussed herein, a shell material depositing or forming onto a nanoscale wire surface will deposit or form in a way such that the shell material tries to minimize its surface area. The shell material may thus be formed as discontinuous sections, or sections having different cross-sectional areas 30 on the core 20, as it minimizes its surface area. See also Fig. 7A, showing shell deposition on a core as a function of time, or Fig. 2, showing pitches with silicon shells on silicon cores of between about 1 to 10 micrometers. Other pitches are also possible, as discussed herein.

It should be understood that Plateau-Rayleigh instability is not synonymous with Plateau-Rayleigh crystal growth. Generally, Plateau-Rayleigh instability is the transformation of a 1-dimensional liquid-state object into periodically spaced liquid-state

- 11 -

spheres, where the pitch is limited to about 4 times the diameter of the original liquid object. This can be observed, for example, in a stream of water from a faucet that eventually breaks apart into separated droplets. This breaking up into droplets is Plateau-Rayleigh instability. Plateau-Rayleigh crystal growth, however, is the growth of a solid-state crystal on solid-state objects, such as solid-state 1-dimensional objects, where the pitch between these shells is determined by the reaction conditions.

5

10

15

20

25

30

As mentioned, various aspects of the present invention are generally directed to nanoscale wires having a core and one or more shell regions surrounding at least a portion of the core. The core is typically a nanowire, or other suitable nanoscale wire such as those discussed herein. In one set of embodiments, the core has at least one cross-sectional dimension and, in some embodiments, two orthogonal cross-sectional dimensions (e.g., a diameter) of less than 1 micrometer, less than about 500 nm, less than about 200 nm, less than about 150 nm, less than about 100 nm, less than about 70, less than about 50 nm, less than about 20 nm, less than about 10 nm, less than about 5 nm, than about 2 nm, or less than about 1 nm. In some embodiments, the core is generally cylindrical. In other embodiments, however, other shapes are possible; for example, the core can be faceted, i.e., the core may have a polygonal cross-section. The cross-section of a core can be any arbitrary shape, including, but not limited to, circular, square, rectangular, annular, polygonal, or elliptical, and may be a regular or an irregular shape. The core may be solid or hollow. In some embodiments, the core may have a substantially uniform profile or cross-sectional area, or have a variation in average diameter of less than about 30%, less than about 25%, less than about 20%, less than about 15%, less than about 10%, or less than about 5%.

In some cases, the nanoscale wire forming the core has one dimension that is substantially longer than the other dimensions of the nanoscale wire. For example, the nanoscale wire may have a longest dimension that is at least about 1 micrometer, at least about 3 micrometers, at least about 5 micrometers, or at least about 10 micrometers or about 20 micrometers in length, and/or the nanoscale wire may have an aspect ratio (longest dimension to shortest orthogonal dimension) of greater than about 2:1, greater than about 3:1, greater than about 4:1, greater than about 5:1, greater than about 75:1, greater than about 75:1, greater than

5

10

15

20

25

30

- 12 -

about 100:1, greater than about 150:1, greater than about 250:1, greater than about 500:1, greater than about 750:1, or greater than about 1000:1 or more in some cases.

The core may be formed out of any of a wide variety of materials. For instance, in one set of embodiments, the core may comprise or consist essentially of a semiconductor material. However, it should be understood that the core can comprise other materials as well in other embodiments of the invention. For example, in one set of embodiments, the core may comprise or consist essentially of a metal. In some cases, at least about 80%, at least about 85%, at least about 90%, at least about 95%, or 100% of the core (by mass) is a metal. Non-limiting examples of potentially suitable metals include aluminum, gold, silver, copper, molybdenum, tantalum, titanium, nickel, tungsten, chromium, platinum, or palladium. Techniques for producing metal nanoscale wires are known to those of ordinary skill in the art, and include, for instance solution processing techniques such as solution-phase synthesis, template fabrication techniques, chemical vapor deposition (CVD), or the like. In some cases, metal nanowires may be obtained commercially. The core may include one or more than one metals (e.g., alloyed together).

In another set of embodiments, the core may comprise or consist essentially of a dielectric material. For example, the core may comprise a nitride, such as Si<sub>3</sub>N<sub>4</sub>, or the core may comprise an oxide, such as a semiconductor oxide or a metal oxide. In one embodiment, the semiconductor oxide is SiO<sub>2</sub>. In another embodiment, the semiconductor oxide is GeO<sub>2</sub>. In still other embodiments, the oxide may be SeO<sub>2</sub>, SnO<sub>2</sub>, GaO<sub>2</sub>, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, NiO<sub>2</sub>, NiO<sub>3</sub>, BaTiO<sub>3</sub>, SrTiO<sub>3</sub>, Fe<sub>3</sub>O<sub>4</sub>, Fe<sub>2</sub>O<sub>3</sub>, MgO, Cr<sub>2</sub>O<sub>3</sub>, ZnO, MgO, VO<sub>2</sub>, V<sub>2</sub>O<sub>5</sub>, MnO, Co<sub>2</sub>O<sub>3</sub>, Co<sub>3</sub>O<sub>4</sub>, CuO, Cu<sub>2</sub>O, ZrO<sub>2</sub>, BaO, WO<sub>2</sub>, CeO<sub>2</sub>, or the like. The core may also comprise other dielectric materials, such as NdFeB, or any other suitable material that is dielectric. Combinations of any of these are also possible in some cases, e.g., the semiconductor oxide may comprise SiO<sub>2</sub> and GeO<sub>2</sub>, SiO<sub>2</sub> and SeO<sub>2</sub>, etc. In some cases, at least about 80%, at least about 85%, at least about 90%, at least about 95%, or 100% of the core (by mass) is a semiconductor oxide. Techniques for producing semiconductor oxide nanoscale wires that can be used as a core will be known to those of ordinary skill in the art, and include, for instance, solution processing techniques, template fabrication techniques, chemical vapor deposition (CVD), or the like.

5

10

15

20

25

30

In yet another set of embodiments, the nanoscale wire core may comprise or consist essentially of a polymer. Examples of polymers include, but are not limited to, polyaniline, polypyrrole, polythiophene, polystyrene, polypropylene, polyester, poly(methyl methacrylate), polyacrylamide, DNA, RNA, SU-8, poly(p-phenylene vinylene), poly(vinylchloride), nylon (e.g., nylon 6, nylon 6,6, etc.), polyurethane, silk, polyphosphazene, low density polyethylene, high density polyethylene, polypropylene, thermoplastic polyurethanes, polychlorotrifluoroethylene, polyvinylidene fluoride, polyvinylidene chloride, polysiloxane, polyethylene, polytetrafluoroethylene, poly(ethylene terephthalate), poly(ethylene oxide), and/or derivatives thereof, etc. In some cases, at least about 80%, at least about 85%, at least about 90%, at least about 95%, or 100% of the core (by mass) is a polymer. Polymeric nanoscale wires that can be used as a core can be prepared using techniques known to those of ordinary skill in the art, such as solution processing techniques, template fabrication techniques, chemical polymerization techniques, etching techniques such as ion etching or plasma etching, or by sol-gel chemistry, etc.

In still another set of embodiments, the nanoscale wire core may comprise or consist essentially of a semiconductor material. For example, the nanoscale wire may comprise silicon. In some cases, the nanoscale wire may comprise germanium. Other suitable semiconductor materials include those discussed herein. In some cases, at least about 80%, at least about 85%, at least about 90%, at least about 95%, or 100% of the core (by mass) is a semiconductor. Typically, a semiconductor is an element having semiconductive or semi-metallic properties (i.e., between metallic and non-metallic properties). Non-limiting examples include elemental semiconductors, such as silicon, gallium, germanium, diamond (carbon), tin, selenium, tellurium, boron, or phosphorous. In other embodiments, more than one element may be present, for example, gallium arsenide, gallium nitride, indium phosphide, cadmium selenide, etc. Still other examples include a Group II-VI material (which includes at least one member from Group II of the Periodic Table and at least one member from Group VI, for example, ZnS, ZnSe, ZnSSe, ZnCdS, CdS, or CdSe), or a Group III-V material (which includes at least one member from Group III and at least one member from Group V, for example GaAs, GaP, GaAsP, InAs, InP, AlGaAs, or InAsP).

- 14 -

Any suitable technique may be used to produce a semiconductor nanoscale wire core, including etching techniques such as ion etching or plasma etching, vapor-liquid-solid (VLS) synthesis, chemical vapor deposition (CVD) techniques, solution-phase synthesis, supercritical fluid-liquid-solid growth, or techniques such as those disclosed in U.S. Pat. No. 7,211,464 incorporated herein by reference in its entirety. As another example, the core may be grown from substantially uniform nanoclusters or particles, e.g., colloid particles. See, e.g., U.S. Patent No. 7,301,199, issued November 27, 2007, entitled "Nanoscale Wires and Related Devices," by Lieber, *et al.*, incorporated herein by reference in its entirety. Other techniques suitable for producing nanoscale wires are also known to those of ordinary skill in the art.

5

10

15

20

25

30

In certain embodiments, the semiconductor can be undoped or doped (e.g., p-type or n-type). For example, in one set of embodiments, a nanoscale wire may be a p-type semiconductor nanoscale wire or an *n*-type semiconductor nanoscale wire. In some embodiments, a dopant or a semiconductor may include mixtures of Group IV elements, for example, a mixture of silicon and carbon, or a mixture of silicon and germanium. In other embodiments, the dopant or the semiconductor may include a mixture of a Group III and a Group V element, for example, BN, BP, BAs, AlN, AlP, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InN, InP, InAs, or InSb. Mixtures of these may also be used, for example, a mixture of BN/BP/BAs, or BN/AlP. In other embodiments, the dopants may include alloys of Group III and Group V elements. For example, the alloys may include a mixture of AlGaN, GaPAs, InPAs, GaInN, AlGaInN, GaInAsP, or the like. In other embodiments, the dopants may also include a mixture of Group II and Group VI semiconductors. For example, the semiconductor may include ZnO, ZnS, ZnSe, ZnTe, CdS, CdSe, CdTe, HgS, HgSe, HgTe, BeS, BeSe, BeTe, MgS, MgSe, or the like. Alloys or mixtures of these dopants are also be possible, for example, (ZnCd)Se, or Zn(SSe), or the like. Additionally, alloys of different groups of semiconductors may also be possible, for example, a combination of a Group II-Group VI and a Group III-Group V semiconductor, for example,  $(GaAs)_x(ZnS)_{1-x}$ . Other examples of dopants may include combinations of Group IV and Group VI elemnts, such as GeS, GeSe, GeTe, SnS, SnSe, SnTe, PbO, PbS, PbSe, or PbTe. Other semiconductor mixtures may include a combination of a Group I and a Group VII, such as CuF, CuCl, CuBr, CuI, AgF, AgCl, AgBr, AgI, or the like. Other dopant compounds may include different mixtures of these

5

10

15

20

25

30

elements, such as  $BeSiN_2$ ,  $CaCN_2$ ,  $ZnGeP_2$ ,  $CdSnAs_2$ ,  $ZnSnSb_2$ ,  $CuGeP_3$ ,  $CuSi_2P_3$ ,  $Si_3N_4$ ,  $Ge_3N_4$ ,  $Al_2O_3$ ,  $(Al, Ga, In)_2(S, Se, Te)_3$ ,  $Al_2CO$ ,  $(Cu, Ag)(Al, Ga, In, Tl, Fe)(S, Se, Te)_2$  and the like.

The doping of the semiconductor to produce a *p*-type or *n*-type semiconductor core may be achieved via bulk-doping in certain embodiments, although in other embodiments, other doping techniques (such as ion implantation) can be used. Many such doping techniques that can be used will be familiar to those of ordinary skill in the art, including both bulk doping and surface doping techniques. A bulk-doped article (e.g. an article, or a portion or region of an article) is an article for which a dopant is incorporated substantially throughout the crystalline lattice of the article, as opposed to an article in which a dopant is only incorporated in particular regions of the crystal lattice at the atomic scale, for example, only on the surface or exterior. For example, some articles are typically doped after the base material is grown, and thus the dopant only extends a finite distance from the surface or exterior into the interior of the crystalline lattice. It should be understood that "bulk-doped" does not define or reflect a concentration or amount of doping in a semiconductor, nor does it necessarily indicate that the doping is uniform. "Heavily doped" and "lightly doped" are terms the meanings of which are clearly understood by those of ordinary skill in the art. In some embodiments, one or more regions comprise a single monolayer of atoms ("deltadoping"). In certain cases, the region may be less than a single monolayer thick (for example, if some of the atoms within the monolayer are absent). As a specific example, the regions may be arranged in a layered structure within the nanoscale wire, and one or more of the regions can be delta-doped or partially delta-doped.

In some embodiments, the nanoscale wire core has a conductivity of or of similar magnitude to any semiconductor or any metal. The nanoscale wire can be formed of suitable materials, e.g., semiconductors, metals, etc., as well as any suitable combinations thereof. In some cases, the nanoscale wire will have the ability to pass electrical charge, for example, being electrically conductive. For example, the nanoscale wire may have a relatively low resistivity, e.g., less than about 10<sup>-3</sup> Ohm m, less than about 10<sup>-4</sup> Ohm m, less than about 10<sup>-6</sup> Ohm m, or less than about 10<sup>-7</sup> Ohm m. The nanoscale wire can, in some embodiments, have a conductance of at least about 1

microsiemens, at least about 3 microsiemens, at least about 10 microsiemens, at least about 30 microsiemens, or at least about 100 microsiemens.

5

10

15

20

25

30

The nanoscale wire core can be solid or hollow, in various embodiments. As used herein, a "nanotube" is a nanoscale wire that is hollow, or that has a hollowed-out core, including those nanotubes known to those of ordinary skill in the art. As another example, a nanotube may be created by creating a core/shell nanowire, then etching away at least a portion of the core to leave behind a hollow shell. Accordingly, in one set of embodiments, the nanoscale wire is a non-carbon nanotube. In contrast, a "nanowire" is a nanoscale wire that is typically solid (i.e., not hollow). Thus, in one set of embodiments, the nanoscale wire may be a semiconductor nanowire, such as a silicon nanowire.

In one set of embodiments, the nanoscale wire may include a heterojunction, e.g., of two regions with dissimilar materials or elements, and/or the same materials or elements but at different ratios or concentrations. The regions of the nanoscale wire may be distinct from each other with minimal cross-contamination, or the composition of the nanoscale wire can vary gradually from one region to the next. The regions may be both longitudinally arranged relative to each other, or radially arranged (e.g., as in a core/shell arrangement) on the nanoscale wire. Each region may be of any size or shape within the wire. The junctions may be, for example, a p/n junction, a p/p junction, an n/n junction, a p/i junction (where i refers to an intrinsic semiconductor), an n/i junction, an i/i junction, or the like. The junction can also be a Schottky junction in some embodiments. The junction may also be, for example, a semiconductor/semiconductor junction, a semiconductor/metal junction, a semiconductor/insulator junction, a metal/metal junction, a metal/insulator junction, an insulator/insulator junction, or the like. The junction may also be a junction of two materials, a doped semiconductor to a doped or an undoped semiconductor, or a junction between regions having different dopant concentrations. The junction can also be a defected region to a perfect single crystal, an amorphous region to a crystal, a crystal to another crystal, an amorphous region to another amorphous region, a defected region to another defected region, an amorphous region to a defected region, or the like. More than two regions may be present, and these regions may have unique compositions or may comprise the same compositions. As one example, a wire can have a first region having a first composition, a second region

- 17 -

having a second composition, and a third region having a third composition or the same composition as the first composition. Non-limiting examples of nanoscale wires comprising heterojunctions (including core/shell heterojunctions, longitudinal heterojunctions, etc., as well as combinations thereof) are discussed in U.S. Patent No. 7,301,199, issued November 27, 2007, entitled "Nanoscale Wires and Related Devices," by Lieber, *et al.*, incorporated herein by reference in its entirety.

5

10

15

20

25

30

In one set of embodiments, the nanoscale wire core is formed from a single crystal, for example, a single crystal nanoscale wire comprising a semiconductor. A single crystal item may be formed via covalent bonding, ionic bonding, or the like, and/or combinations thereof. While such a single crystal item may include defects in the crystal in some cases, the single crystal item is distinguished from an item that includes one or more crystals, not ionically or covalently bonded, but merely in close proximity to one another. The single crystal may be one that contains no grain boundaries, although it may contain defects, dislocations, impurities, etc. in some cases. However, in other embodiments, the core may be composed of crystallites, the core may be polycrystalline or single crystalline, etc.

In some embodiments, the nanoscale wires used herein are individual or free-standing nanoscale wires. For example, an "individual" or a "free-standing" nanoscale wire may, at some point in its life, not be attached to another article, for example, with another nanoscale wire, or the free-standing nanoscale wire may be in solution. This is in contrast to nanoscale features etched onto the surface of a substrate, e.g., a silicon wafer, in which the nanoscale features are never removed from the surface of the substrate as a free-standing article. This is also in contrast to conductive portions of articles which differ from surrounding material only by having been altered chemically or physically, *in situ*, i.e., where a portion of a uniform article is made different from its surroundings by selective doping, etching, etc. An "individual" or a "free-standing" nanoscale wire is one that can be (but need not be) removed from the location where it is made, as an individual article, and transported to a different location and combined with different components to make a functional device such as those described herein and those that would be contemplated by those of ordinary skill in the art upon reading this disclosure.

5

10

15

20

25

30

- 18 -

The core may be surrounded by one or more shell materials. These shell materials may be deposited or formed onto the core, in one aspect of the invention, by deposition techniques where a fluid, such as a liquid and/or a gas, flows or passes by a core, e.g., in a longitudinal direction relative to the core, as is shown in Fig. 7B. Some of the shell material (or a precursor of the shell material) can deposit on the core, e.g., to form one or more shells surrounding at least a portion of the core. This deposition may not necessarily occur uniformly. Rather, the deposition of the shell materials or precursors may be performed under conditions that cause nonuniform deposition or formation of the shell materials. For instance, the shell materials may deposit or form as a series of discontinuous regions separated by regions of the core that do not contain any deposits (or any substantial deposits) of the shell material. In some cases, the shell materials or precursors may deposit such that the surface area is relatively minimized and the shell material is concentrated or located in certain regions along the core. For instance, as discussed in more detail below, reaction conditions may be applied to create conditions in which the shell material seeks to minimize surface area, e.g., such that Plateau-Rayleigh crystal growth occurs.

The shell regions may be discontinuous and separated along the nanoscale wire in certain embodiments. For instance, one shell region may be separated from its next nearest shell region by a distance along the core of at least about 1 nm, at least about 3 nm, at least about 5 nm, at least about 7 nm, at least about 10 nm, at least about 15 nm, at least about 30 nm, at least about 50 nm, at least about 75 nm, at least about 100 nm, at least about 200 nm, at least about 300 nm, at least about 500 nm, at least about 750 nm, at least about 1 micrometer, at least about 2 micrometers, at least about 3 micrometers, at least about 4 micrometers, at least about 5 micrometers, at least about 6 micrometers, at least about 7 micrometers, at least about 8 micrometers, at least about 10 micrometers, at least about 15 micrometers, at least about 20 micrometers, at least about 30 micrometers, at least about 50 micrometers, at least about 75 micrometers, or more in some cases. In some cases, the distance of separation may be no more than about 100 micrometers, no more than about 75 micrometers, no more than about 50 micrometers, no more than about 30 micrometers, no more than about 20 micrometers, no more than about 15 micrometers, no more than about 10 micrometers, no more than about 8 micrometers, no more than about 7 micrometers, no more than about 6 micrometers, no more than about 5

micrometers, no more than about 4 micrometers, no more than about 3 micrometers, no more than about 2 micrometers, no more than about 1 micrometer, no more than about 750 nm, no more than about 500 nm, no more than about 300 nm, no more than about 50 nm, no more than about 100 nm, no more than about 75 nm, no more than about 50 nm, no more than about 30 nm, no more than about 15 nm, no more than about 10 nm, no more than about 7 nm, no more than about 5 nm, or no more than about 3 nm.

Combinations of any of these are also possible; for instance, two shell regions may be separated by a distance of separation between about 1 micrometer and about 5 micrometers.

5

10

15

20

25

30

In some cases, the shells may be substantially regularly spaced along the core. It should be understood that in reality, the spacing may not necessarily be perfect, but there may be some variation in the spacing. The average spacing between shells may be referred to as the "pitch" of the shells, and is usually measured from the leading edge of one shell region to the leading edge of the next shell region (see, e.g., Fig. 1A). Multiple such distances may also be averaged together to determine the average pitch. In some embodiments, the pitch may fall within any of the ranges given above for the distance of separation, e.g., in one set of embodiments, the pitch may be between about 1 micrometer and about 5 micrometers. However, as mentioned, it should be understood that the average spacing or pitch is an average, and individual shell regions may be closer or farther away. For instance, there may be a standard deviation or variation of at least about 3%, at least about 5%, at least about 10%, at least about 15%, at least about 20%, at least about 25% of the mean value of the pitch.

These shell regions may be spherical in some embodiments (which would represent an idealized minimal state), but in other embodiments, the regions can be non-spherical. For instance, in some cases, the shell material (or precursor thereof) may deposit as a crystal, and in some cases, the depositions may be monocrystalline or substantially monocrystalline, e.g., without discrete domains or grain boundaries within a single shell region. Thus, in some embodiments, a shell region is a single crystal. In some cases, due to the crystallinity, the regions may deposit non-spherically. For example, as is shown in Fig. 3D, the regions may deposit with generally square or rectangular cross-sectional areas, or with areas having an aspect ratio (i.e., of two dimensions orthogonal to the longitudinal direction) of at least about 1.3:1, at least about

- 20 -

1.5:1, at least about 1.8:1, at least about 2:1, at least about 2.5:1, at least about 3:1, at least about 4:1, at least about 5:1, etc.

5

10

15

20

25

30

In some cases, the shell regions comprise a portion that has a substantially uniform cross-sectional area, relative to the longitudinal direction along the nanoscale wire core. Optionally, the regions may also comprise portions that do not have a uniform cross-sectional area, which can be understood to be a transition portion, e.g., as shown in a cross-sectional view in Fig. 13B. In some embodiments, a shell region may have a portion having a uniform cross-sectional area having a maximum dimension (orthogonal to the core) of greater than about 10 nm, greater than about 30 nm, greater than about 50 nm, greater than about 75 nm, greater than about 100 nm, greater than about 150 nm, greater than about 200 nm, greater than about 250 nm, greater than about 300 nm, greater than about 350 nm, greater than about 400 nm, greater than about 450 nm, greater than about 500 nm, greater than about 600 nm, greater than about 700 nm, greater than about 800 nm, greater than about 900 nm, greater than about 1 micrometer, greater than about 2 micrometers, greater than about 3 micrometers, greater than about 4 micrometers, or greater than about 5 micrometers. In addition, in some cases, the dimension may be less than about 5 micrometers, less than about 4 micrometers, less than about 3 micrometers, less than about 2 micrometers, less than about 1 micrometer, less than about 900 nm, less than about 800 nm, less than about 700 nm, less than about 600 nm, less than about 500 nm, less than about 450 nm, less than about 400 nm, less than about 350 nm, less than about 300 nm, less than about 250 nm, less than about 200 nm, less than about 100 nm, less than about 75 nm, less than about 50 nm, less than about 30 nm, less than about 10 nm, etc. Combinations of any of these are also possible in some embodiments; for instance, a shell region may have a dimension orthogonal to the core of between about 100 nm and about 400 nm. In addition, as mentioned, the shell material may also have a substantially circular cross-sectional area, or have other geometries or other various aspect ratios. Dimensions of the core are discussed elsewhere herein, and can be combined with any of these dimensions (or other dimensions as described herein) of the shell, in certain embodiments.

The shell regions may also have a length determined longitudinally along the core of at least about 1 nm, at least about 3 nm, at least about 5 nm, at least about 7 nm, at least about 10 nm, at least about 15 nm, at least about 50 nm, at

5

10

15

20

25

30

- 21 -

least about 75 nm, at least about 100 nm, at least about 200 nm, at least about 300 nm, at least about 500 nm, at least about 750 nm, at least about 1 micrometer, at least about 2 micrometers, at least about 3 micrometers, at least about 4 micrometers, at least about 5 micrometers, at least about 6 micrometers, at least about 7 micrometers, at least about 8 micrometers, at least about 10 micrometers, at least about 15 micrometers, or more in some cases. In some cases, the length may be no more than about 20 micrometers, no more than about 15 micrometers, no more than about 10 micrometers, no more than about 8 micrometers, no more than about 7 micrometers, no more than about 6 micrometers, no more than about 5 micrometers, no more than about 4 micrometers, no more than about 3 micrometers, no more than about 2 micrometers, no more than about 1 micrometer, no more than about 750 nm, no more than about 500 nm, no more than about 300 nm, no more than about 200 nm, no more than about 100 nm, no more than about 75 nm, no more than about 50 nm, no more than about 30 nm, no more than about 15 nm, no more than about 10 nm, no more than about 7 nm, no more than about 5 nm, or no more than about 3 nm. Combinations of any of these are also possible. For example, in one embodiment, the shell may have a length of between about 1 micrometer and about 2 micrometers.

In certain embodiments, the nanoscale wire (including the core and shell) has a maximum dimension, orthogonal to the core, of less than about 5 micrometers, less than about 4 micrometers, less than about 3 micrometers, less than about 2 micrometers, less than about 1 micrometer, less than about 900 nm, less than about 800 nm, less than about 700 nm, less than about 600 nm, less than about 500 nm, less than about 450 nm, less than about 400 nm, less than about 350 nm, less than about 300 nm, less than about 250 nm, less than about 100 nm, less than about 50 nm, less than about 50 nm, less than about 30 nm, less than about 50 nm, less than about 30 nm, less than about 10 nm, etc.

In some embodiments, the shell region may also contain one or more transition portions, e.g., regions that do not have a uniform cross-sectional area. Typically, the transition portion may be positioned between the shell region and regions of the nanoscale wire core that are substantially free of such shell portions (or have smaller shell portions). In some cases, the transition portion may have a length, determined along the core, of at least about 5 nm, at least about 10 nm, at least about 20 nm, at least about 30 nm, at least about 50 nm, at least about 100 nm, etc. In addition, in certain

embodiments, the transition portion may have a length of no more than about 100 nm, no more than about 50 nm, no more than about 30 nm, no more than about 20 nm, no more than about 10 nm, etc. These may also be combined together in certain embodiments. For example, the transition portion of the shell region may have a longitudinal length of between about 10 nm and about 30 nm.

5

10

15

20

25

30

For instance, referring to Fig. 13B, a nanoscale wire may comprise a plurality of periodic shell regions 30 surrounding a core, where the shell regions are separated by regions 37. The shell regions may comprise a first portion 33 with a substantially cross-sectional area, and a second transition portion 36 that does not have a substantially cross-sectional area. It should be understood that Fig. 13B is a schematic diagram, and the transition portions may not necessarily be perfectly linear or crystalline. See, e.g., Fig. 1C for examples of nanoscale wires having transition portions. In addition, in some embodiments, there may not be separate shell regions surrounding the core, but instead the shell regions may be present as having variations in thickness, e.g., as is shown in Fig. 13C with first portions 33 and second portions 34 around core 20. One or both portions may have substantially uniform cross-sectional areas, where first portion 33 is larger than second portion 34. These may also be periodically spaced in some embodiments, e.g., at the pitches described herein.

The shell regions may be formed out of any suitable material, and may independently be the same or different from the core. For instance, the shell region may comprise a semiconductor (e.g., silicon, germanium, indium phosphide, etc.), a semiconductor oxide (e.g., silicon dioxide), a metal (e.g., Ni, Pt, Au, etc.), a polymer (e.g., polyaniline, polypyrrole, etc.), or the like. Examples of these and other materials have been previously described above. In addition, in some cases, the shell region may be present as a single crystal. The shell region may also be substantially crystalline, substantially monocrystalline, polycrystalline, single crystalline, or composed of crystallites, etc. In addition, it should be noted that the crystallinity of the core and of the shell may independently be the same or different.

It addition, it should be noted that in some cases, fabricating core and shell regions with different materials results in lattice mismatches, especially where the core and the shell are crystalline or monocrystalline. In some embodiments, under conditions such as Plateau-Raleigh crystal growth, long surface diffusion length of the shell material

on the surface of the nanoscale wire may be required in some embodiments, which could potentially result in failure of the shell material to deposit on the surface of the nanoscale wire. However, surprisingly, it has been found that under some conditions, e.g., with relatively small shell regions, non-homogenous deposition can still occur despite the lattice mismatches.

5

10

15

20

25

30

In addition, in one set of embodiments, the shell region may comprise a plurality of nanoparticles. For instance, as discussed below, in one set of embodiments, a fluid containing nanoparticles may be passed along a nanoscale wire, and nanoparticles may deposit onto the nanoscale wire, forming shell regions of nanoparticles around the nanoscale wire, such as is shown in Fig. 14.

In some cases the nanoparticles may have an average diameter of less than about 1 mm, less than about 500 micrometers, less than about 200 micrometers, less than about 100 micrometers, less than about 75 micrometers, less than about 50 micrometers, less than about 25 micrometers, less than about 10 micrometers, or less than about 5 micrometers in some cases. The average diameter may also be at least about 1 micrometer, at least about 2 micrometers, at least about 3 micrometers, at least about 5 micrometers, at least about 10 micrometers, at least about 15 micrometers, or at least about 20 micrometers in certain cases. The nanoparticles may be, for example, metallic, polymeric, ceramic, or the like. Examples of polymeric nanoparticles include, but are not limited to, poly(methyl methacrylate), poly(vinyl alcohol), poly(acrylic acid), polyacrylamide, polymethacrylic acid, polycaprolactone, polylactide, polyglycolide, etc. Examples of metallic nanoparticles include, but are not limited to, gold, silver, copper, platinum, or palladium nanoparticles. Many such nanoparticles are commercially available.

Another aspect of the present invention is generally directed to systems and methods of making nanoscale wires as discussed herein. In one set of embodiments, a fluid containing a shell material (or precursor thereof) is deposited onto a nanoscale wire, or other suitable nanoscale wire. The fluid may be, for example, a liquid, a gas, a plasma, or the like. Combinations of these are also possible, e.g., a mixture of gas and liquid.

A variety of different techniques may be used to flow a material past a nanoscale wire, including physical vapor deposition, CVD, thermal evaporation, liquid flow,

sputtering, e-beam evaporation, plasma CVD, or the like. For example, in some embodiments, one or more shell materials (or precursors) are first vaporized into the gaseous phase (e.g., via heat or temperature, chemical reaction, e-beam evaporation, etc.), then the material passes over the nanoscale wire and some of the material deposits onto the nanoscale wire. For example, silane (SiH<sub>4</sub>) may deposit onto the nanoscale wire as Si, germane (GeH<sub>4</sub>) may deposit onto the nanoscale wire as Ge, etc. In another set of embodiments, the shell materials (or precursors) may be dissolved or suspended in solution, and deposit onto the surface of the nanoscale wire, e.g., physically or chemically. For example, nanoparticles such as those discussed herein may be suspended in aqueous solution then passed over a nanoscale wire.

5

10

15

20

25

30

As a non-limiting example, in one set of embodiments, a shell material (or precursor thereof) may be deposited onto a nanoscale wire using chemical vapor deposition (CVD). For instance, shell material or precursor may flow past the nanoscale wire (e.g., in a fluid, and/or in vacuum) at a flowrate of less than about 20 sccm, less than about 15 sccm, less than about 10 sccm, less than about 5 sccm, etc. In some cases, the temperature may be at least about 600 °C, at least about 650 °C, at least about 700 °C, at least about 750 °C, at least about 850 °C, at least about 900 °C, at least about 950 °C, etc. In some cases, the temperature may be less than about 1000 °C, less than about 950 °C, less than about 950 °C, less than about 850 °C, less than about 850 °C, less than about 850 °C, less than about 950 °C, etc. Combinations of these are also possible; for instance, the temperature may be between about 700 °C and about 900 °C.

In addition, in some cases, the shell material or precursor may be propelled under vacuum conditions or pressures (e.g., when contained in a fluid). For example, the pressures may be pressures of less than about 100 torr (absolute), less than about 50 torr, less than about 30 torr, less than about 10 torr, less than about 5 torr, less than about 3 torr, less than about 1 torr, etc. In some cases, the fluid may comprise gases such as  $H_2$ ,  $N_2$ ,  $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$ ,  $A_5$

In one set of embodiments, the shell material or precursor (e.g., in a vacuum, or contained in a fluid) is passed or flowed across the core such that some of the shell material (or precursor) is able to deposit on the core, e.g., to form one or more shell regions. After deposition of the shell material onto the surface, in some cases, there may be some lateral diffusion of the shell material, i.e., on the surface. Under some

conditions, once the shell material (or precursor) deposits onto the core (or onto deposited shell materials), the shell material (or precursor) does not immediately become immobilized, but may be able to diffuse on the surface to some extent. For instance, the surface diffusion length of the shell material on the surface of the nanoscale wire may be at least about 5 nm, at least about 10 nm, at least about 30 nm, at least about 50 nm, at least about 750 nm, at least about 100 nm, at least about 300 nm, at least about 750 nm, at least about 1000 nm, etc. The surface diffusion length may be determined using techniques known by those of ordinary skill in the art including, for instance, field ion microscopy or scanning tunneling microscopy. In addition, in some embodiments, the surface diffusion length may be estimated using:

$$\Lambda = a \sqrt{\frac{V_{os} n_o}{J_r}} e^{-E_s/2RT}$$

5

10

15

20

25

where lambda ( $\Lambda$ ) is the diffusion length, alpha ( $\alpha$ ) is the adatom hop distance, or the distance between two neighboring equilbrium positions of adatoms while they are diffusing, nu ( $\nu_{os}$ ) is a pre-exponential frequency factor,  $n_o$  is the areal density of adsorption sites,  $J_r$  is the deposition flux of the precursor gas onto the surface,  $E_s$  is the activation energy for diffusion, R is the gas constant, and T is the temperature.

If the surface diffusion length of the shell material is relatively large, and/or if the shell material has the ability to diffuse along the surface of the nanoscale wire, then in some cases, the diffusion of the shell material on the surface of the nanoscale wire (e.g., on the core and/or the shell material) may occur such that the shell material reaches a lower energy state where its exposed surface area is minimized. Surprisingly, the minimal state does not occur when the core is uniformly coated with a homogeneous shell, but instead, the minimal state is a state where the shell material is concentrated in certain regions (generally spherical) along the core, for instance, where a given surface area encompasses the largest possible internal volume. It is surprising that such a phenomenon could be exploited in the nanoscale wire context to produce nanoscale wires having non-uniformly deposited shell, as is discussed herein, or in other solid materials. Plateau-Rayleigh crystal growth has not previously been observed in solids, or in the growth of crystals on a solid object, e.g., on the core of a nanowire.

Another aspect of the present invention includes the ability to fabricate essentially any electronic device from any of the nanoscale wires discussed herein, for a variety of applications, including but not limited to electronics, optical, thermal, or mechanical applications. This includes any device that can be made in accordance with 5 this aspect of the invention that one of ordinary skill in the art would desirably make. Examples of such devices include, but are not limited to, field effect transistors (FETs), bipolar junction transistors (BJTs), tunnel diodes, modulation doped superlattices, complementary inverters, light emitting devices, light sensing devices, biological system imagers, biological and chemical detectors or sensors, thermal or temperature detectors, 10 Josephine junctions, nanoscale light sources, photodetectors such as polarization-sensitive photodetectors, gates, inverters, AND, NAND, NOT, OR, TOR, and NOR gates, latches, flip-flops, registers, switches, clock circuitry, static or dynamic memory devices and arrays, state machines, gate arrays, and any other dynamic or sequential logic or other digital devices including programmable circuits. Also included 15 are analog devices and circuitry, including but not limited to, amplifiers, switches and other analog circuitry using active transistor devices, as well as mixed signal devices and signal processing circuitry. Also included are p/n junction devices with low turn-on voltages; p/n junction devices with high turn-on voltages; and computational devices such as a half-adder. In some embodiments, the nanoscale wires of the present invention 20 may be manufactured during the device fabrication process. In other embodiments, the nanoscale wires of the present inventions may first be synthesized, then assembled in a device.

In some cases, the device may be a nanoscale transistor, such as a field effect transistor ("FET") or a bipolar junction transistor ("BJT"). The transistor may have a smallest width of less than 500 nm, less than 100 nm, or other widths as described herein. Any transistor constructed using adjacent regions having different compositions, are contemplated, for example, arranged longitudinally within a single wire, arranged radially within the wire, or the like. In one embodiment, a FET comprising a nanoscale wire may serve as a conducting channel, and an elongated material having a smallest width of less than 500 nm (e.g., a nanoscale wire) serving as the gate electrode. For such a FET, the widths of the nanoscale wire may define a width of the FET. Further, the nanoscale wire may comprise a semiconductor, or have a core/shell arrangement, and

25

30

- 27 -

such shell may function as a gate dielectric for the FET. In one embodiment, the transistor may be a coaxially-gated transistor.

5

10

15

20

25

30

Such distinct nanometer-scale metrics may lead to significantly improved device characteristics such as high gain, high speed, and low power dissipation. Further, such FETs may be readily integratable, and the assembly of such FETs may be shrunk in a straightforward manner into nanometers scale. Such a "bottom-up" approach may scale down to sizes far beyond what is predicted for traditional "top-down" techniques typically used in the semiconductor industry today. Further, such bottom-up assembly may prove to be far cheaper than the traditional top-down approach.

Electronic devices incorporating semiconductor nanoscale wires may be controlled, for example, using any input signal, such as an electrical, optical or a magnetic signal. The control may involve switching between two or more discrete states or may involve continuous control of nanoscale wire current, i. e., analog control.

The following documents are incorporated herein by reference: U.S. Pat. Nos. 7,129,554, 7,211,464, 7,256,466, 7,301,199, 7,476,596, 7,595,260, 7,666,708, 7,915,151, and 8,153,470; Int. Pat. Apl. Pub. Nos. WO 02/17362, WO 02/48701, and WO 03/005450; and Int. Pat. Apl. No. PCT/US2014/014596, filed February 4, 2014, entitled "Anisotropic Deposition in Nanoscale Wires," by Lieber, *et al.* In addition, U.S. Provisional Patent Application Serial No. 61/989,904, filed May 7, 2014, entitled "Controlled Growth of Nanoscale Wires," by Lieber, *et al.* is incorporated herein by reference.

The following examples are intended to illustrate certain embodiments of the present invention, but do not exemplify the full scope of the invention.

# **EXAMPLE 1**

The Plateau-Rayleigh (PR) instability, as described by Joseph Plateau and Lord Rayleigh in the mid-1800s, describes how a thin column of water can break apart into droplets to minimize its surface tension. The following examples describe certain processes using PR instability to control the growth of crystals on 1-dimensional (1D) materials, a process termed Plateau-Rayleigh Crystal Growth (PRCG). In these examples, Si is deposited onto uniform-diameter Si nanowire (NW) cores to generate diameter-modulated core/shell NW structures. Similarly, Ge can be deposited onto uniform-diameter Ge NW cores. Distinct morphological features of these structures are

broadly tunable through rational control of reaction conditions for crystalline shell growth. Analysis of the results reveals that an understanding of both thermodynamic/surface energy driving forces and kinetic control of reaction rates of PR Crystal Growth are necessary to explain the broad range of modulated structures. To date, the design and synthesis of the vast majority of nanoscale wire structures has relied primarily on two general paradigms: axial modulation during core growth and radial modulation during shell growth; PR Crystal Growth represents a fundamentally new general paradigm for generating diameter-modulated nanoscale wire structures with complex morphologies of various materials and sizes.

5

10

15

20

25

30

At elevated temperatures, 1D NW cores can serve as starting materials for several distinct processes. The introduction of reactive gases can lead to the conformal deposition of crystalline shells as can be seen in Fig. 1A, left. Annealing at low pressures and without reactant gases can transform various NWs into periodically spaced, isolated crystals due to PR instability (Fig. 1A, top). In contrast to conformal deposition, the introduction of reactant gases at lower pressures yields diameter-modulated, periodic shell (PS) NWs with several well-defined morphological features (Fig. 1A, right), including various cross-sectional aspect ratios (AR, or the ratio of the outer diameter to the outer height); modulation amplitudes (ratio of outer diameter to inner diameter); and modulation pitches (length of one inner and outer shell). Importantly, these morphological features are synthetically tunable, as they are sensitive

to the reaction conditions used for shell deposition. Although PR instability and PR Crystal Growth both lead to periodically spaced structures starting from 1D materials, they are distinct phenomena; traditional PR instability describes constant volume transformations (i.e. not growth processes) and does not afford tunability in morphology.

The following examples illustrate conformal core/shell growth, PR instability and PRCG. For these examples, Si NW cores with diameters of 100 nm and lengths of 10 to 60 micrometers were first grown via a Au-catalyzed VLS process by chemical vapor deposition (CVD) at 465 °C. See, e.g., U.S. Pat. Nos. 7,211,464; 7,301,199; 7,476,596; 7,595,260; 7,666,708; 7,915,151; or 8,153,470, each incorporated herein by reference.

For the first growth, shell growth at 775  $^{\circ}$ C, with a SiH<sub>4</sub> partial pressure of ~100 mtorr, and a H<sub>2</sub> partial pressure of ~25 torr for ~15 minutes, yielded highly-crystalline, axially-uniform core/shell nanoscale wires. In a second experiment, after core growth,

the temperature was increased to > 775 °C and the total pressure was reduced to ~ 0.1 torr. SEM images (Fig. 1B, left) revealed that the cores transformed into particles. The time scales for transformation depended on temperature and core diameter. At 775 °C, 100 nm cores began to break up after > 14 hours (Fig. 5); at 900 °C, the 1D to 0D transformation was complete within 3 minutes (Fig. 1B, left). Fig. 5 shows an annealed 100 nm Si core NW. SEM image of a representative 100 nm Si core NW that was annealed at 775 °C for ~ 14 hours at ~ 0.2 torr directly following core growth. Scale bar, 200 nm. In a third synthesis, following the growth of 100 nm cores, a SiH<sub>4</sub> partial pressure of ~1 mtorr was introduced at 775 °C for ~15 minutes. Head-on SEM images (Fig. 1B, right) revealed NWs with low aspect ratios and diameter modulations that periodically repeat along the axis of the NWs.

To demonstrate the tunability of PRCG, separate core/shell syntheses were performed in which the cores were the same size and grown in the same manner; however, the temperature and/or partial pressure of  $SiH_4$  used during shell growth was varied. Plan-view SEM images (Fig. 1C) of NWs transferred to  $Si_3N_4$ -coated  $Si_3N_4$

15

20

25

30

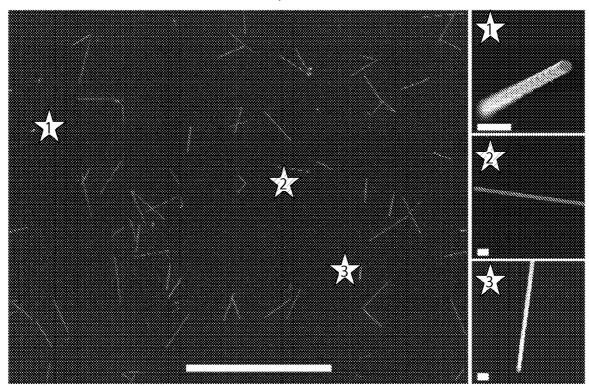

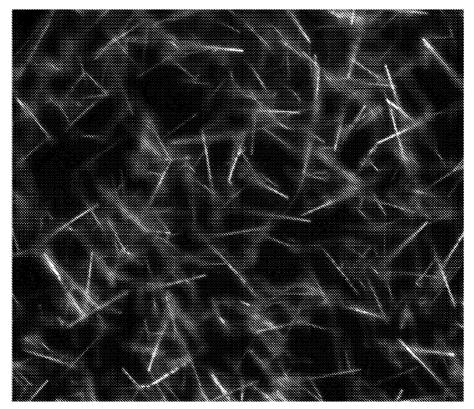

Fig. 6 shows yield of diameter-modulated NWs. Fig. 6A shows, left, SEM image of an approximately 300 x 250 micrometer<sup>2</sup> area from a PS NW growth substrate. Higher-magnification SEM images of NWs denoted by stars are shown on the right. Scale bar, 10 micrometers. Right, high resolution SEM images of the single NWs denoted in the wide area image to the left. Stars 1 and 3 indicate representative images of NWs that clearly have diameter modulations; Star 2 indicates a NW without clear diameter modulation from SEM imaging. Examining all of the NWs in the large area region indicates that the yield of diameter-modulated NWs is ~90%. Scale bars, 1 micrometers. Fig. 6B shows optical dark field image of a PS NW growth substrate. The image was recorded using a 20x objective and an extra 1.6x magnifying lens; subsequently, the color tone of the entire image was adjusted in Adobe Photoshop to reduce the background in order to provide the best contrast for the diameter-modulation of the NWs to be visible.